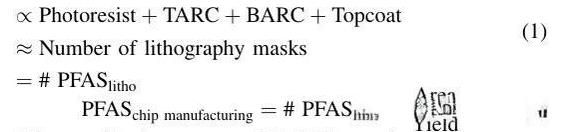

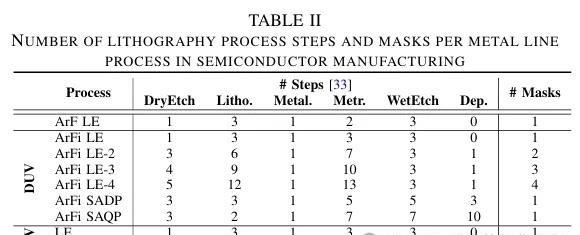

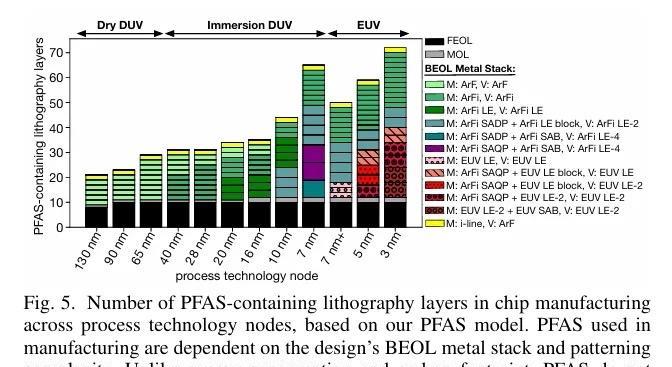

PFAS与半导体制造分析模型 半导体制造中PFAS的使用量高度依赖图案化复杂性和金属层堆叠。图展示了半导体制造中最常用光刻工艺(包括光刻-刻蚀(LE)、自对准双重图案(SADP)和自对准四重图案(SAQP))的工艺复杂性和含PFAS层。根据工艺流程和使用的化学品,PFAS的量以及抗反射涂层、旋涂涂层和顶层涂层与特定光刻胶的组合使用情况会有所不同。例如,某工艺流程可能仅包含BARC和光刻胶。我们的模型为设计师和工程师提供了更新和定制给定工艺节点的图案化复杂性和工艺流程的灵活性,允许集成用户定义的制造规范。 我们的PFAS模型基于中提出的金属堆叠,并根据通常使用含PFAS光刻胶、ARCs、顶层涂层和其他涂层的光刻步骤,估算含PFAS层的数量。在半导体制造中,掩模用于在硅晶圆上光刻图案化特征,因此我们使用光刻掩模数量作为代理来估算制造中使用的PFAS量(表2)。PFAS分析建模公式为: 我们量化了130nm至3nm工艺节点半导体制造中的PFAS使用量。图显示了芯片制造中前端(FEOL)、中端(MOL)和后端(BEOL)的含PFAS光刻层数量。含PFAS层的数量随着集成电路制造中光刻步骤的增加而增加。与DUV相比,使用直接EUV技术可减少含PFAS层数,这对应更少的掩模数量和工艺步骤。#半导体EDA# 然而,随着特征尺寸缩小,由于更先进工艺节点的复杂性增加,掩模和光刻步骤的数量也会增加。